Pada komputer bertingkat modern, n mungkin lagi untuk mengisolasi rangkaian divisi karena tidak ada divisi sirkuit. Semua instructins tersedia di tingkat mechine konvensional dilakukan satu langkah pada suatu waktu oleh seorang juru bahasa berjalan pada tingkat microprogramming.

Review of the digital logic level (Tinjauan tingkat logika digital)

T Tugas microprogrammer adalah untuk menulis sebuah program untuk mengendalikan mesin register, bus, ALUs, kenangan, dan komponen perangkat keras lainnya.

1. Register : perangkat yang mampu menyimpan informasi mendaftar. Tingkat microprogramming selalu memiliki beberapa register yang tersedia untuk terus memerlukan informasi untuk memproses instruksi saat ini sedang ditafsirkan. Secara konseptual, register sama dengan memori utama, perbedaan yang yang mendaftarkan secara fisik terletak di dalam prosesor itu sendiri, sehingga mereka dapat dibaca dari dan disimpan menjadi lebih cepat bahwa kata-kata dalam memori utama, yang biasanya off-chip. Pada komputer yang sama sekelompok register nomor 0,1, 2, ..., n - 1, tersedia pada tingkat microprogramming, dan disebut penyimpanan lokal atau penyimpanan papan penggaris.

Gambar 1

r egister A dapat dicirikan dengan satu nomor: berapa banyak bit dapat terus.

2. Buses : bus adalah kumpulan kabel yang digunakan untuk mengirim sinyal secara paralel. Bus digunakan karena transfer paralel semua bit sekaligus jauh transmisi serial pada suatu waktu sedikit. Sebuah bus mungkin searah atau bidirectional. Sebuah bus searah hanya dapat mentransfer data dalam satu arah tapi tidak keduanya secara bersamaan. Unidireksional bus biasanya digunakan untuk menghubungkan dua register, salah satu yang selalu menjadi sumber dan yang lain yang selalu tujuan.

Gambar 2

3. Multiplexer and decoders : sirkuit yang memiliki lini satu atau lebih masukan dan menghitung nilai-nilai satu atau lebih output yang unik ditentukan oleh input sekarang disebut sirkuit kombinasional. Dua yang paling penting adalah multiplexer dan decoder. Sebuah plexer multi memiliki input data 2n, salah satu data masukan dari lebar sama dengan masukan, dan n-bit input kontrol yang memilih salah satu masukan dan rute ke output.

Gambar 3

Kebalikan dari multiplekser adalah sebuah demultiplexer, yang rute input tunggal untuk salah satu output 2n nya, tergantung pada calue pada baris n kontrol.

4. ALU and shifters : irkuit yang paling sederhana adalah hanya sebuah penambah, yang mengambil dua input n-bit dan menghasilkan jumlah sebagai output. Sebuah rangkaian aritmatika yang lebih umum adalah ALU atau unit logis aritmetika. Ini juga memiliki input data dua dan satu output data, tetapi juga memiliki kendali input dan output.

Gambar 4

5. Cloks : rangkaian komputer biasanya didorong oleh sebuah jam, sebuah perangkat yang memancarkan urutan periodik pulsa. Pulsa ini mendefinisikan siklus mesin. Pada setiap siklus mesin, terjadi beberapa kegiatan, seperti pelaksanaan amicroinstruction. Hal ini sering berguna untuk membagi siklus ke subcycles, bagian sangat berbeda dari microinstruction dapat dilakukan dalam urutan yang baik-Devine. Sebagai contoh, masukan ke ALU harus tersedia dan diperbolehkan menjadi stabil sebelum output dapat disimpan.

Gambar 5

6. Main memory : prosesor harus mampu membaca data dari memori dan menulis data ke memori. Sebagian besar komputer memiliki bus alamat, bus data dan bus kontrol untuk komunikasi antara memori CPU. Untuk membaca dari memori, CPU menempatkan alamat memori pada bus alamat dan mengatur sinyal kendali tepat, misalnya, dengan menegaskan (READ). Memori menempatkan item yang diminta pada bus data. Dalam beberapa memori komputer membaca / menulis adalah sinkron, yaitu, memori harus merespon dalam waktu yang tetap. Pada orang lain, memori dapat berlangsung selama yang diinginkan, menandakan adanya data menggunakan garis kontrol ketika fineshed.

Gambar 6

7. Component packaging (pengkemasan komponen) : sirkuit ini tersedia secara komersial beberapa aku bentuk konseptual yang berbeda. Cara yang paling mudah adalah dalam bentuk paket integrasi skala menengah, dengan setiap chip berisi komponen. Sebagai contoh sebuah register, sebuah ALU, atau sebuah shifter.

Gambar 7

Kelemahan utama untuk membangun sebuah komputer dari bagian MSI adalah jumlah besar keripik diperlukan, yang papan manya occuoy, mengkonsumsi banyak daya, dan menghilangkan panas yang signifikan.

Microarchitecture

1. Data path : jalur data adalah bagian dari CPU yang berisi ALU, masukan OTS, dan output-nya. Ini mengandung 16 register identik 16 bit, berlabel PC, AC, SP, dan seterusnya, bahwa dari memori papan penggaris hanya bisa diakses ke tingkat microprogramming.

Gambar 8

ALU output masuk ke shifter, yang dapat mengubahnya 1 arah baik, ot tidak sama sekali. Its mungkin untuk melakukan suatu pergeseran kiri 2-bit register, R, dengan menghitung R + R di ALU (yang merupakan bergeser ke kiri 1-bit), dan kemudian jumlah pergeseran bit kiri lain menggunakan shifter tersebut.

2. Microinstructions : ini dapat dibagi ke sembilan kelompok fungsional, seperti dijelaskan dibawah.

16 sinyal untuk mengontrol beban bus A dari papan penggaris

16 sinyal untuk mengontrol beban bus B dari papan penggaris

16 sinyal untuk mengontrol pemuatan papan penggaris dari bus C

2 sinyal untuk mengontrol A dan B kait

2 sinyal untuk mengontrol fungsi ALU

2 sinyal untuk mengontrol shifter yang

4 sinyal untuk mengontrol MAR dan MBR

2 sinyal untuk mengindikasikan membaca memori dan memori menulis

1 sinyal untuk mengontrol Amux

siklus terdiri dari gaiting nilai-nilai ke bus A dan B, menempel mereka di bus dua selot, menjalankan nilai-nilai melalui ALU dan shifter, dan akhirnya menyimpan hasil di papan penggaris dan / atau MBR. Selain itu, MAR juga dapat di-load, dan memulai siklus memori. Sebagai pendekatan afirst, kita bisa memiliki kontrol register 61-bit, dengan satu bit untuk setiap sinyal kontrol. A bit 1 berarti bahwa sinyal menegaskan dan 0 berarti bahwa itu dinegasikan.

microinstruction ini berisi 13 bidang, 11 di antaranya adalah sebagai berikut:

AMUX: kontrol kiri input ALU: 0 + A latch, 1 = MBR

ALU: ALU fungsi: 0 = A + B, 1 = A dan B, 2 = A, 3 = A '

SH: fungsi shifter: 0 = shift tidak, 1 = kanan, 2 = kiri

MBR: beban MBR dari shifter

MAR: moads MAR dari B latch

RD: memori permintaan membaca

WR: memori permintaan menulis

Enc: kontrol menyimpan ke scarchpad

C: mendaftar dipilih untuk menyimpan ke dalam jika enc = 1: 0

B: memilih sumber bus B

J: Sebuah bus memilih sumber

Gambar 9

3. waktu Microinstruction: peristiwa penting selama setiap dari empat subcycles adalah sebagai berikut:

• Muat microinstruction berikutnya yang akan dieksekusi menjadi sebuah register yang disebut MIR, Register MicroInstruction.

• Gerbang mendaftar ke bus A dan B dan menangkap mereka di A dan B kait

• Sekarang masukan stabil, memberikan ALU dan waktu shifter untuk menghasilkan ANF beban output stabil MAR jika diperlukan.

• Sekarang shifter keluaran stabil, toko bus C di papan penggaris dan beban MBR, jika salah satu diperlukan.

Gambar 10

4. Sekuensing Microinstruction: hanya sisa masalah adalah bagaimana microinstruction berikutnya dipilih. Meskipun beberapa waktu yang cukup hanya untuk mengambil microinstruction berikutnya adalah urutan, mekanisme beberapa perlu untuk memungkinkan kondisional dalam microprogram agar memungkinkan untuk membuat keputusan. Untuk alasan ini kami telah menyediakan dua bidang di setiap microinstruction, ADDR, yang merupakan pengganti alamat potensial untuk microinstruction saat ini, dan cond, yang menentukan apakah microinstruction selanjutnya adalah mengambil dari MPC + 1 atau ADDR. Pilihan yang diinginkan ditandai dengan penetapan bidang cond sebagai berikut:

0 = tidak melompat; microinstruction berikutnya diambil dari MPC + 1

1 = loncat ke ADDR jika N = 1

2 = loncat ke ADDR jika Z = 1

3 = melompat ke ADDDR tanpa syarat.

Logika urutan mikro menggabungkan dua bit ALU, N dan Z dan dua bit cond, kal tem L dan R untuk kiri dan kanan, untuk menghasilkan sebuah output. Sinyal yang benar adalah

Mmux = L’RN + LR’Z+LR=RN+LZ+LR

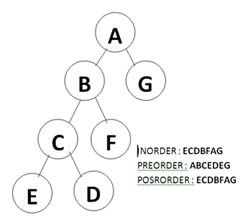

INORDER, PREORDER, POSTORDER PADA POHON BINER

Jika INFIX, PREFIX, POSTFIX, digunakan pada stack maka INORDER, PREORDER, POSTORDER, digunakan pada kunjungan pohon biner.

Cara gampang untuk mengingat nya adalah:

1. Kunjungan secara Inorder/infix (Symmetric order) mempunyai urutan:

kiri, akar, kanan

inorder(node)

if node.left ≠ null then inorder(node.left)

print node.value

if node.right ≠ null then inorder(node.right)

—————————————————————-

2. Kunjungan secara preorder/prefix (Depth First Order)

akar, kiri, kanan

preorder(node)

print node.value

if node.left ≠ null then preorder(node.left)

if node.right ≠ null then preorder(node.right)

—————————————————————-

3. Kunjungan secara postorder/postfix

kiri , kanan, akar

postorder(node)

if node.left ≠ null then postorder(node.left)

if node.right ≠ null then postorder(node.right)

print node.value

—————————————————————-

CATATAN

Link penjelasan gerbang logika http://lafalofe.blogspot.com/2009/03/gerbang-logika.html

link gambar gerbang logika http://elektronika-elektronika.blogspot.com/2007/05/gerbang-logika-logic-gate.html

Sistem komputer

Empat komponen dalam system computer , yi :

1. Pemroses

• untuk mengendalikan operasi computer & melakukan fugnsi pemrosesan data

• pemroses melakukan operasi logika dan mengelola aliiran data dgn membaca instruksi dari memori & mengeksekusinya

• langkah kerja pemroses :

o mengambil instruksi biner dari memori

o mengkode isntruksi menjadi aksi sederhana

o melakukan aksi.

3Operasi computer :

1. operasi aritmatika (ADD, SUBTRACT, MULTIPLY, DEVIDE)

2. Operasi Logika (NAND, XOR, OR, AND, INVERTION)

3. Operasi Pengendalian (Loop, JUMP).

Pemroses tdd :

1. Alu (Aritmathic Logic Unit) utk melakukan operasi aritmatika dan logika

2. CU (Control Unit) utnuk mengendalikan operasi yagn dilaksanakan system computer

3. Register2 memiliki fungsi :

Membantu pelaksanaan operasi yagn dilakukan pemorses.

Sebagai memori yagn berkerja sec cepat, biasanay untuk tempat operand2 dr operasi yagn akan dilakukan

Terbagi menjadi register data & reg alamat

Reg data tdd general & special purpose register.

Reg alamat berisis : alamat data dan main memory, alamat isntruksi, alamat untuk perhit alamat lengkap, contoh : reg Indeks, register penunjuk segmen, register penunjuk stack, register penanda (flag).

Register

Pemrosessan melakukan tugasnya dengan mengeksekusi instruksi2 di program dgn mekanisme instruksi sbb :

a. Pemroses membaca isntruksi dari memori (fetch)

b. Pemroses mengeksekusi isntruksi (execute)

Eksekusi prog berisi pengulangan fetch & execute. Pemrrosesan satu instruksi dsb satu siklus instruksi (instructioncycle)

Gambar siklus ekseksui instruksi

Memori

1. Berfungsi menyimpan data & prog

2. Biasanya vollate, data hilang jika sumber tenaga hilang

3. Konsep prog tersimpan stored program concept) yi prog (Kumpulan isntruksi) yang disimpan di suatu temapt (emmori) dimana kmdn disntruksi tsbt dieksekusi.

Setiap kali pemroses melakukan ekseskusi, pemroses harus membaca isntruksi dari memori utama. Agar eksekusi dilakukan sec cepat mk harus diusahakan isntruksi tersedia. Di memori pd lapisan berkecepatn lbh tinggi. Kec eksekusi ini akan meningkatakn kinerja system.

Hirarki memori berdasarkan kec akses :

1. Register (tercepat)

2. Cache memory (kec akses lbh cepat dari main memory ttp dibawah register)

Memori berkapasitas terbatas, kec tinggi yang lbh mahal dibandung main memory. Cache adalah diantara main memory & reg, shg pemroses tidak langsung mengacu memori utama ttp di cache memory yang kec akses lbh tinggi.

3. Main Memory

4. Disck Chare (Buffering) bgn memori utama utk menampung data yagn akan ditransfer dari / ke perangkat I/O & penyimpanan sekunder shg menignkat kinerja system. Miss : magnetic disc, optical s\disc (terlambat)

Perangkat I/O

1. Perangkat nyata yang dikendalikan choip controller di board system / card

2. Controller dihub dgn pemroses & komponen lainya melalui BUS

3. Controller mempunyai register2 utnuk pengendalianya yg berisi status kendali

4. Tiap controller dibuat agar dapat dilamati sec individu olh pemroses shg perangkat lunak device driver dpt menulis ke register2 ny shg dapat diekndalikan.

Gates and Boolen Algebra

sirkuit digital dapat dibangun dari sejumlah kecil elemen primitif dengan menggabungkan mereka dengan cara yang tak terhitung banyaknya. Pada bagian berikut kita akan menggambarkan unsur-unsur primitif, shiw bagaimana mereka dapat dikombinasikan, dan memperkenalkan teknik matematika canggih yang dapat digunakan untuk menganalisis perilaku mereka.

Gerbang

Suatu sirkuit digital yang hanya satu dua nilai logis yang hadir. Biasanya, sinyal antara 0 dan 1 volt merupakan salah satu nilai (misalnya, biner 1) dan sinyal antara 2 dan 5 volt merupakan nilai lainnya (misalnya, biner 1). Tegangan di luar kedua merebak tidak diijinkan. Tiny perangkat elektronik, disebut gerbang, dapat menghitung berbagai fungsi kedua-nilai sinyal. Ini sinyal-sinyal dari dasar hardware di mana semua komputer digital dibangun.

Semua logika digital modern akhirnya bersandar pada fakta bahwa transsistor dapat dibuat untuk beroperasi sebagai saklar biner sangat cepat. Dalam ara. 3-1 (a) kami telah menunjukkan sebuah transistor bipolar tunggal (lingkaran) tertanam di sirkuit sederhana. transistor ini memiliki tiga koneksi ke dunia luar: kolektor, basis, dan emitor itu. Ketika tegangan masukan, Vin di bawah nilai kritis tertentu, transistor dimatikan dan bertindak seperti sebuah perlawanan yang tak terbatas, menyebabkan output dari sirkuit, Vout, untuk membuat di dekat nilai Vcc, tegangan eksternal diatur, biasanya + 5 volt. Ketika Vin melebihi nilai kritis, transistor switch pada bertindak seperti kawat, menyebabkan vout harus ditarik ke tanah (oleh Konvensi, 0 Volt).

Gambar. 3-1.(a) a transistor inverter (b)A NAND gate. (c) A NOR gate.

Kesimpulan : aljabar Bool adalah aljarbar yang dimana variabelnya adalah 0 dan 1.

Hal penting untuk diperhatikan adalah bahwa ketika Vin rendah, Vout tinggi, dan sebaliknya. Sirkuit ini demikian inverter, mengkonversi 0 logis ke 1 logis, dan logis 1-0 logis. resistor ini diperlukan untuk membatasi jumlah arus yang ditarik oleh transistor. Waktu yang diperlukan untuk beralih dari satu negara ke lainnya dalam adalah biasanya sebuah beberapa nanodetik.

Dalam ara. 3-1 (b) dua transistor yang mengalir secara seri. Jika kedua v1 dan v2 tinggi. Jika input baik rendah, transistor terkait akan menonaktifkan, dan output akan menjadi tinggi. Dengan kata lain, Vout akan rendah jika dan hanya jika kedua V1 dan V2 tinggi.

Dalam ara 3-1 (c) kedua input rendah, output akan tetap tinggi.

Jika sekarang kita mengadopsi konvensi bahwa "tingginya" (Vcc volt) adalah 1 logis dan yang "rendah" (tanah) adalah logis 0, kita dapat mengekspresikan nilai output sebagai fungsi dari nilai-nilai input.

Kesimpulan : aljabar yg dimana variabelnya adalah 0 dan 1

Boolean Algreba

Sebuah fungsi Boolean memiliki satu atau lebih variabel input dan menghasilkan hasil yang tergantung hanya pada nilai-nilai variabel-variabel ini. Sebuah fungsi f sederhana, dapat didefinisikan dengan mengatakan bahwa f (A) adalah 1 jika A adalah 0 dan f (A) o jika A adalah 1. Fungsi ini adalah fungsi NOT ara. 3-2 (a).

Karena fungsi Boolean variabel n hanya memiliki 2n mungkin set nilai-nilai input, fungsi tersebut dapat sepenuhnya dijelaskan dengan memberikan meja dengan 2n baris, setiap baris menceritakan nilai fungsi untuk kombinasi yang berbeda dari nilai input.

Selama dua variabel dalam, urutan 00 01, 10, 11, fungsi tersebut dapat sepenuhnya dijelaskan oleh 2n - jumlah bit biner diperoleh dengan membaca kolom hasil dari tabel kebenaran secara vertikal. Jadi NAND os 1110, NOR adalah 1000, DAN adalah 0.001, dan OR adalah 0.111. Jelas, hanya 16 boolean fungsi dari dua variabel keluar, sesuai dengan hasil yang mungkin 16 string 4-bit. Sebaliknya, aljabar biasa memiliki jumlah tak terbatas fungsi dari dua variabel, tidak ada yang dapat dijelaskan dengan memberikan sebuah tabel output untuk semua masukan mungkin karena setiap variabel dapat mengambil salah satu dari jumlah nilai yang mungkin tak terbatas.

Multiplexers

Suatu rangkaian pada level logika digital yang mempunyai input data Zm , output data & input control dimana salah satu dari data input Zm yagn dipilih dari remote control n diarahkan ke output.

Pada tingkat logis digital, multiplekser adalah sebuah sirkuit dengan 2n input data, satu output data, dan input n kontrol yang pilih salah satu masukan data. Input data yang dipilih adalah "gerbang" (yaitu, diarahkan) ke output. Gambar 3 -12 adalah diagram skematik untuk multiplekser delapan-masukan. Garis kontrol tiga, A, B dan C, mengkodekan nomor 3-bit yang menentukan yang mana dari delapan baris input adalah pintu gerbang ke gerbang OR dan dari situ untuk output. Tidak peduli apa nilai ada di saluran kontrol, tujuh dari gerbang DAN akan selalu output0; output mungkin lain baik 0 atau 1, tergantung pada nilai baris masukan terpilih. Setiap gerbang DAN diaktifkan oleh kombinasi yang berbeda dari masukan kontrol.

Kita telah melihat bagaimana sebuah chip multiplexer dapat digunakan untuk memilih salah satu dari beberapa masukan dan bagaimana dapat menerapkan tabel kebenaran. Aplikasi lain adalah sebagai konverter data paralel-to-serial. Dengan meletakkan 8 bit data pada baris input dan kemudian melangkah garis kontrol secara berurutan 000-111 (biner), 8 bit diletakkan ke baris output secara seri.

Gambar

Fig 3-12 an Eight multiplexer circuit

Decoders

Sebuah rangkaian yang memperoleh nomr n bit sbg input & meng alur tsbt ntuk memilih jalur salah satu output dari Zn

Untuk melihat mana decoder mungkin berguna, bayangkan memori yang terdiri dari delapan chip, setiap mengandung 8K bytes. Chip 0 memiliki alamat 0-8091, chip alamat telah 8.192-16.383 dan seterusnya. Ketika alamat disajikan ke memori, urutan tinggi 3 bit yang digunakan untuk memilih salah satu dari delapan chip

Comparators

MSi chip lain yang berguna adalah pembanding, yang membandingkan dua kata masukan. Pembanding sederhana, yang membandingkan dua kata masukan. Sederhana pembanding pada Gambar. 3-15 mengambil dua input, A dan B setiap panjang 4 bit, dan menghasilkan 1 jika mereka adalah sama dan 0 jika tidak sama. rangkaian ini didasarkan pada gerbang XOR, yang menempatkan sebuah 0 jika input nya adalah sama dan 1 jika mereka tidak setara. Jika dua kata masukan adalah sama, keempat gerbang XOR harus output 0. Keempat sinyal kemudian dapat ORed bersama-sama, jika hasil 0. kata-kata input adalah sama, jika tidak. Dalam contoh kami kelinci menggunakan gerbang NOR sebagai tahap akhir membalikkan rasa tes: 1 berarti sama, 0 berarti tidak setara. MSI chip yang tersedia secara komersial pembanding tidak hanya hav pin untuk A = B, tetapi juga pin untuk A B.

Gambar

Fig 3-14 A 3-to-8 Decoder Circuit

Programmed Logic Arrays

Sebuah chip yang sangat umum untuk membentuk jumlah produk adalah array logika atau PLA diprogram, contoh kecil yang ditunjukkan pada Gambar. 3-16. Chip ini, yang 74S330, memiliki baris input untuk 12 variabel. Komplemen dari setiap masukan yang dihasilkan secara internal, membuat sinyal masukan 24 dalam semua. Inti dari rangkaian tersebut adalah sebuah array 50 DAN gerbang, masing-masing jika yang berpotensi dapat memiliki subset dari 24 sinyal input sebagai input. Yang sinyal input yang masuk ke gerbang AND ditentukan oleh matriks 24x50 sedikit disediakan oleh pengguna. Setiap baris input ke 50 DAN gerbang berisi sumbu. Ketika dikirimkan dari pabrik, semua 1200 sekering utuh untuk program matriks pengguna luka bakar sekering keluar yang dipilih dengan menggunakan tegangan tinggi untuk chip.

Aritmathic logical units (ALU)

Sebagian besar komputer berisi sirkuit tunggal untuk melakukan AND, OR, dan jumlah dari dua kata mesin. Biasanya, seperti rangkaian kata-kata n-bit dibangun daftar imbuhan n identik sirkuit untuk posisi bit individual. Hal ini dapat komputer salah satu dari empat fungsi - yaitu, A DAN B, A OR B ', A + B, tergantung pada apakah fungsi F0 baris input-pilih dan F1 mengandung 00,01,10, atau 11 (biner)

Sudut kiri bawah kita ALU berisi decoder 2 bit untuk menghasilkan baris memungkinkan untuk operasi 4, berdasarkan F0 dan F1. Sudut kiri atas memiliki logika untuk menghitung A DAN B, A OR B, dan B, tapi paling banyak satu hasil ini dilewatkan ke gerbang OR final, tergantung pada untuk mengaktifkan baris keluar dari decoder. Karena tepat satu output decoder akan 1, tepat satu dari empat DAN gerbang gerbang OR mengemudi mengemudi gerbang OR akan mengaktifkan 3 lainnya akan menampilkan 0, independen dari A dan B.

Aritmathic Circuit

Tidak ada waktu untuk beralih dari rangkaian tujuan umum MSI dibahas di atas untuk MSI sirkuit kombinasional digunakan untuk melakukan aritmatika. Kita akan mulai dengan shifter 8 bit yang sederhana, lalu melihat bagaimana adders dibangun, dan akhirnya memeriksa unit logis aritmetika, yang memainkan peran sentral dalam komputer mana pun.

Shifter

pertama kita sirkuit aritmatika MSI adalah input delapan, delapan output shifter (pada Gambar 3-17). Delapan bit input disajikan pada garis D0, ...., D7. Output yang hanya masukan bergeser sedikit pun, tersedia pada garis S0, ...., S7. Garis kontrol C, menentukan arah perubahan, 0 untuk kiri dan 1 untuk benar.

Untuk melihat bagaimana rangkaian bekerja, perhatikan pasang DAN gerbang untuk semua bit kecuali gerbang pada akhir. Ketika C = 1, anggota hak setiap pasangan dihidupkan, melewati sedikit input ke output yang sesuai. Karena hak DAN gerbang adalah kabel ke input gerbang OR ke kanan, sebuah pergeseran yang benar dilakukan. Ketika C = 0, itu adalah anggota pasangan kiri gerbang AND yang menyala, yang mempengaruhi pergeseran kiri.

Adders

Komputer yang tidak dapat menambahkan bilangan bulat tak terpikirkan. Akibatnya, sirkuit FOT melakukan kecanduan merupakan bagian penting dari setiap CPU. Tabel kebenaran untuk penambahan 1-bit yang ditunjukkan pada Gambar. 3-18 (a). dua output yang hadir, jumlah input, A dan B, dan membawa ke tingkat berikutnya (ke kiri) posisi. Sebuah rangkaian untuk komputasi baik jumlah dan membawa dapat dilihat pada Gambar. 3-18 (b). sirkuit ini adalah mengetahui sebagai penambah setengah.

Meskipun penambah setengah cukup untuk menjumlahkan bit low-order dari dua kata multibit masukan, itu WLL tidak melakukan untuk posisi bit pada tengah kata tersebut karena tidak menangani membawa ke posisi dari kanan. Sebaliknya, penambah penuh Gambar 3-19 diperlukan. Dari rangkaian pemeriksaan harus jelas bahwa penambah penuh dibangun dari dua setengah adders. Baris jumlah output adalah 1 jika ganjil A, B dan Carry di adalah 1. Yang melakukan adalah 1 jika salah A dan B keduanya 1 (kiri masukan ke gerbang OR) atau tepat satu dari mereka adalah 1 dan bit Carry di juga 1. Bersama alamat setengah dua menghasilkan baik jumlah dan membawa bit.

Aritmathics Logical Unit

Sebagian besar komputer berisi sirkuit tunggal untuk melakukan DAN, ATAU dan jumlah dua kata mesin. Biasanya, seperti rangkaian kata-kata n-bit yang dibangun dari rangkaian n identik untuk posisi bit individual. Gambar 3-20 adalah contoh sederhana seperti sebuah rangkaian, disebut unit logis aritmathic atau ALU. Hal ini dapat menghitung salah satu dari empat fungsi-yaitu, A DAN B, A OR B, B ', ATAU A + B, tergantung pada apakah fungsi pilih baris input F0 dan F1 conatin 00,01,10 Atau 11 (biner)

Fotocopyan terjemahan

Struktur organisasi Prosesors

Hal2 yg dilakukan CPU

1. fetch instruction mengambil interupsi

Cpu membaca interupsi dari memori

2. Interupt Instruction Menerjemahkan Interupsi

Iterupsi hrs dikodekan utk mennetukan aksi apa yg diperlukan.

3. Fetch data Mengambil data

Eksekusi dari instruksi memerlukan pembacaan data dr memori I/O

4. Proses data memproses data ( mengolah data)

ekseskusi suatu interupsi memeerlukan operasi logika & aritmatika thdp data.

5. Write Data menulis data

Hasil eksekusi memrlukan penulis data bukan dr memori ttp ke memori.

Agar dpt melakukaan hal2 tersebut CPU perlu penyimpanan data utk sementara waktu. CPU hrs mengingat lokasi instruksi terakhir shg CPU akn mengambil instruksi berikutnya.

CPU memerlukan memori internal yg berukuran kecil

CPU dengan Bus sistem

2 fungsi register

1. User Visible reg reg memungkinka memprog bhs mesin & assambler meminimalkan main memory dgn cara mengoptimalakn penggunaan register.

2. Status & Control Register reg2 ini digunakan olh unit control utk mengontrol operasi CPU oleh prog sistem operasi utk mengkontrol eksekusi prog.

USER VISIBLE REGISTER

register yg dpt direfresentasikan dgn mengg bhs mesin yg dieksekusi CPU, secara virtual semua rancangan CPU memiliki user visible reg yg mrpkn kebalikan akumulator tunggal

PerbeDaaNnya:

1. General Purpose reg dpt digunakan utk fungsi2 pengalamatan register indirect (pengalamatan) dan Disclassccemen

2. Reg Data hanya dipakai utk menampung data & tdk dpt digunakan utk kalkulasi & alamat operand

3. Reg alamat menyerupai General Purpose reg perbedaanya digunakan utk mode pengalamatan tertentu.

Cth : Segmen pointer, Register Index, Stack Pointer.

4. Kode bit2 dikumpulkan pada sebuah register membentuk register kontrol dimn instruksi mesin membaca proses kontrol namun tdk dpt diubah ol program.

Pd bgn mesin peanggil sub rutin menyebabkan pengupanan otomatis reg2 user visible, dimn penyimpanan & penggunaan dilakukan CPU sbgm eksekusi instruksi

STATUS CONTROL REGISTER

Empat bh register yg penting bg eksekusi instruksi :

1. Program Counter (PC) berisi isntruksi yg akn diambil

2. Instruction Register (IR) Instruksi yg terkahir akn diambil

3. Memory Addres Register MAR brsi alamat sebuah lokasi di dlm memory

4. Memory Buffer Reg (MBR) berisi sebuah word data yg kan ditulis didlm memory (data yg terkahir di baca)

Command Field / flag :

- Sign berisi bit tanda hsl operasi aritmatika terakhir

- Zero distel bilaa hasil sama dgn 0

- Carry distel apbl operasi yg dilakukan ke dlm carry ke dlm bit yg lebh tinggi / borrow pengurangan bit yg lbh tinggi

- Equall distel apbl perbandingan logika sama

- Overflow megindikasikan proses aritmatika.

- Interupt Enable / Disable mencegah sebuah interupsi

- SuperVision Mengindeikasikan apakah CPU sdg menegksekusi pd daerah2 tertentu dlm memori hanya yg dpt diakses.

Pada umumnya prog ounter du upadate oelh CP saat / setiap mengambil instruksi shg prog counter menunjuk ke berikutnya yg akn dieksekusi data dipertukarkan dgn memori dgn menggunakan MAR & MBR pd sistem organiasi BUS.

MAR terhubung lagsg dgn bus lamat sdgkn MBR terhub langs dgn Bus data

4 fungsi reg diatas :

1. ke 4 reg itu digunakn utk penukaran data dr CPU dgn memory kmdn diberikn ke ALU utk proses selanjutnya, jd Alu dpt mengkases lgsg ke MBR

2. Fungsi lain sbg pertukaran data adlh I/O bagi ALU.

Trdpt bbrp reg lainny yg berkitan dgn suatu & control register yi suatu pointer ke dlm blok memori yg berisi infor status tambahan.

Miss : blok2 kotrol proses

Miss : apabila stack diimplementasi fungsi2 tertentu mk diperukan stack pointer sistem.

Register digunakan dlm pengotrolan I/O

SET INSTRUKSI

Jenis operand tdd :

1.data Transfer (perpindahan data)

A.jenis instruksi mesin adlh jenis transfer data, menetpakan lokasi operand sumber operand tujuan lokasi2 trsbt pd mem reg & bgn plg atas pd stack

B.Menetapkan panjang data yg dipindahkan

C.Menetapkaan mode pengalamatan setiap operand

Set Instruksi tdd :

1. Move (tansfer) perpindahan word / blok dr sumber ke tujuan

2. Store memindahkn word dr prosesor ke memori

3. LOAD memindahkn word dr memory ke prosesor

4. Clear memindahkan NOT ke tuju

5. SET memindahkan word ke tuj

6. PUSH men + kn suatu elemen pd puncak stack, memindahkan word dr sumber ke bgn atas pd stack.

7. POP memimdahkan word dr bn atas stak ke tuj.

2.Aritmatika

Add menghit penjumlahan 2 buah operand.

Substrack menghilangkan 2 buah operand

Multiply menghit perkalian 2 buah operand

Absolure menganti operand dgn nilai absolute

negate mengganti tanda oeprand

Mode Pengalamatan

Mengetesi keterbatasan format instruksi

- dapat mereferensi format instruksi

- Mode pengalamatan yg mampu menangani memori yg bsr

Masing2 prosesor menggunakan mode pengalamatan yg berbeda2

Memiliki pertimabngan dlm penggunaanya

Teknik Pengalamatan

1.Imemediate addreasing

Bentuk pengalamatan in plg sederhana?

a.Operand benar2 ada dlm instruksi / bagian dr instruksi = operand sama dgn field alamat Umumny bil akan disamping dlm bentuk komplemen 2 Bit paling kiri sbg bit tanda Ketika operand dimuatkan ke dlm register data, bit tanda akan digeser ke kiri hingga max word data

Contoh ADD5; Tambahakan 5 pd akumulator

Immadiate Addreasing (+) & (-)

(+) mode ini tidakadanya referensi memori selain dari instruksi yg diperlukan memperoleh operand, menghemeat siklus instruksi shg proses keseluruhan akn cepat

(-) ukuran bil dibatasi olh ukuran field alamat

Direct Addresing (2)

Pengalamatan Langsng

Kelebihan field alamat berisi efektif addres sebuah operand, hanya digunaan pd kom lama & komkecil, hany memrlukan sebuah referensi memori tidak memerlukan kalkulasi khusus

Kelemahan keterbatasan field alamat krn panjang field alamat biasny lbh kecl dibaning panjang word

Contoh ADD A; Tambahkn isi pd lokasi A ke akumulator

Indirect Addresing (3)

Mode pengalamatan tdk langsung

A.Field alamat mengacu pd alamat word di dlm memori, yg plg giliranny akn berisi alamat operand yg panjang

B.Contoh : ADD (A); tambahkn isi memori yg di tunjuk olh si alamat A ke akumulator

Indirect Addreasing (+) & (-)

Keuntungan ruang g alamat menjd besar shg semakn banyak alamat yg dpt referensi

Kerugian diperlukan referensi memori ganda dl suatu fetch shg meperlambat proses operasi

Register Addresing (4)

a.Metode pengalmatan register mirip dgn mode pegalmatan langsung

b.Perbedaanya terletak pd feld alamat yg mengacu pd reg, buka pd memori utama

c.Field yg mereferesi reg memilki panjang 3 / 4 bit, shg dpt mereferensi 8 / 16 reg general purpose

Register Addreasing (+) & (-)

Keuntungan pengalamatan reg Diperlukan field alamat berukuran kecil dlm instruksi & tdk diperukan referensi memori akses ke reg lbh cpt dr pd akses ke memori, shg proses eksekusi akn lbh cpt

Kerugian ruang almat mnjd terbatas

Register Indirect Addreasing

Metode pengalamatan reg tdk lgsung mirip dgn mode pengalamatan tidak langsung

A.Perbedaanny : field alamat mengacu pada alamat reg. Letak operand berada pada memori yg ditunjuk oelh siregister.

B.Keuntungan & keterbatasan pengalamatan reg tidak langsung pd dasarnya sama dgn pegngalamatna tdk lgsung

Keterbatasan field alamat diatasi dgn pengaksesan memori yd tdk langsung shg alamat yg dpt direferensi mkn banyak

Dalam satu siklus pengambilan dan penyimpanan, mode pengalamatan register tidak lngsung hanya mengg satu referensi memori utama shg lbh cpt dari pd mode pengalamatan tidak langsung

Dispalcement Addreasing (6)

A.Menggabungkan kemampuan a pengalamtan langsung & pengalamatan register tidak langsung

B.Mode ini menyaratakan isntruksi memiliki 2 buah field alamat, sedikitny sebuah field yg eksplisit

Field eksplisit bernilai A & field implisit mengarah pd regiset

Oprand berada alamat A ditambah isi reg

Tiga model displacement

Relative addreasing, base reg addreasing, Indexing

Dispalcement Addreasing

Relative addreasing, reg yg direferensi sec implisit adlh prog counter

ke field alamat Memanfaatkan konsep lokaslitas memori utk menyediakan oepran2 berikutnya

Base reg addreasing, reg yg direferensikn berisi sebuha alamat memori. & field alamat berisi perpindahan dari lalat itu. Referensi reg dpt eksplisit maupun implisit Memanfaatkan konsep lakalitas memori.

Indexing adlh field alamat mereferensi alamat memori utama, dan reg direferensikn berisi perpindahan positif dr alamat trsbt

Mrpkn kebaikan dr model base reg

Field almt dianggap sbg almt memori dlm indexing

Manfaat penting dr indexing adlh utk ekseksi program2 interatif

Stack Addreasing (7)

Stack adlh array lokasi yg linier = push down list = LIFO Queue

Stack mrpkn blok lokasi yg terbalik – butir di + kn ke puncak stack shg setiap saat blk akan terisi sec parsial

Yg berkaitan dgn stack adlh pointe yg nilainy mrpkn almt bgn plg atas stack

Dua elemen teratas stack dpt berada d dlm reg CPU, yg dlm hal ini stack pointer mereferensi ke dlm ketiga stack

Stack pointer tetap berada didlm reg

Dgn demikian, referensi2 ke lokasi stack didlm memori pd dasarny mrpkn pengalamatan reg tdk langsung

Mode Pengalamatan Tabel

MODE Algoritma Keuntungan Kerugian

Immediate Operand =A Tidak ada referensi memori Besaran oeprand terbts

Direct eA = A Sederhana Ruang almt terbatas

Indirect eA = (A) Ruang alamat besar Referensi memori ganda

Register eA = R Tdk ad referensi memori Ruang almt terbatas

Register indirect eA = (R) Ruang alamt besar Referensi memori ekstra

Dispacement eA = A + (R) Flesibel Kompleks

stack eA = top of stack Tidak ada referensi Aplikasi memori terbatas

Model pengalamatan Pentium

MODE ALGORITMA

Immadiate Operand = A

Register eA = R

Displacement eA = (SR) + A

Base eA = (SR) + (B)

Base with displacement eA = (SR) + (B) + A

Scaled index with dispalcement eA = (SR) + (B) + (I) + A

Base with scaled index & dispalcement eA = (SR) + (I) X S + (B) + A

relative eA = (PC) + A

Ket :

SR = reg segment PC =prog counter

A =isi field alamat B =reg basis

I = reg indeks S = Faktor skala

Mode pegalamatan pentium

Mode Immediate

Oprnd berada di dlm instruksi

Oprnd dpt berupa data byte, word maupun doubleword

Mode operand reg, operand reg, operand adlh isi reg

Brp macam jenis reg :

Reg 8 bit (AH, BH, CH, DH, AL, BL, CL, DL)

Reg 16 bit (AX,BX,CX,DX,SI,DI,SP,BP)

Reg 32 bit (EAX,EBX,EDX,ESI,EDI,ESP,EBP)

Reg 8,16 dan 32 mrpkn reg utk penggunaan umum

Reg 64 bit biasany utk operasi floating point

Reg segmen (CS,DS,ES,SS,FS,GS)

Mode pengalamtan pentium

Mode displacement

alamat efektif berisi bgn2 instruksi degn displacememnt 8,16 dan 32 bit

dgn segmentasi, slrh almt dlm isntrksi mengacu ke sebuah affset d dlm segment

dlm pentium, mode ini digunakan utk mereferensi varabel2 global

Tidak ada komentar:

Posting Komentar